CPU 내부 구조와 레지스터

CPU 구성요소

중앙 처리 장치 (CPU, Central Processing Unit): 컴퓨터에서 데이터 처리 동작을 수행하는 부분

- 레지스터 세트 (Register set): 명령어를 실행하는 데에 필요한 데이터를 보관

- 산술논리장치 (ALU, Arithmetic Logic Unit): 명령어를 실행하기 위한 마이크로 연산 수행

- 제어장치 (Control Unit) : RS간 정보전송 감시, ALU에게 수행할 동작을 지시

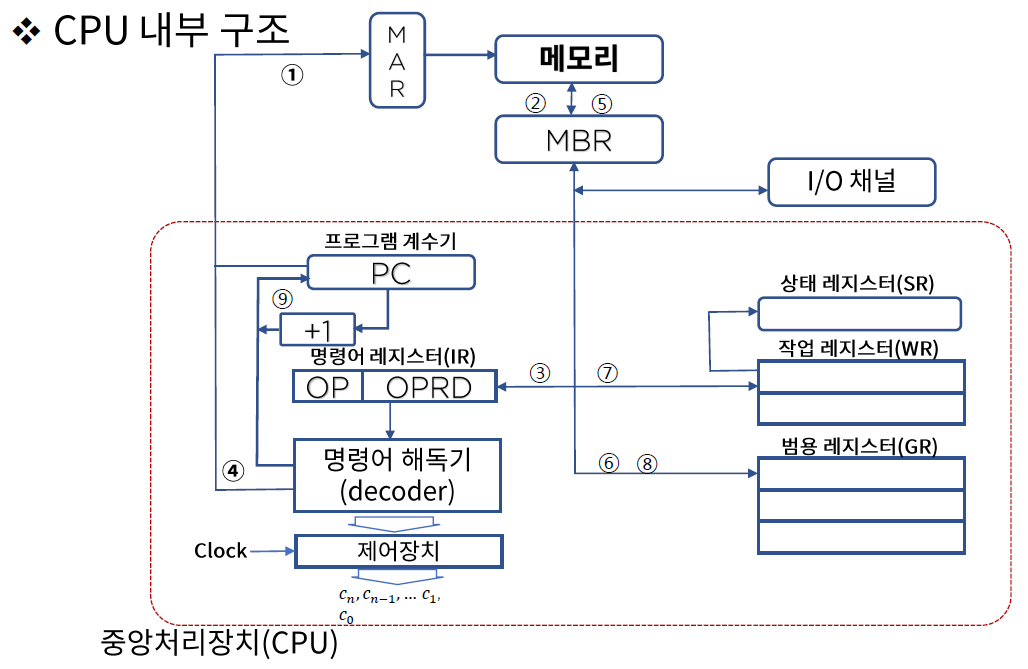

CPU 내부 구조

각종 레지스터들의 명칭과 기능

- MAR (Memory Address Register) : MBR로부터 쓰여지거나 읽혀질 워드의 메모리 주소를 저장

- MBR (Memory Buffer Register) : 메모리에 쓰여질 워드를 가지고 있거나 메모리로부터 읽혀진 워드를 저장

- PC (Program Counter) : 다음에 수행될 명령어가 들어있는 주기억장치의 주소를 저장

- IR (Instruction Register) : PC가 지정하는 주소에 저장되어 있는 명령어를 저장

- ID (Instruction Decoder) : IR에 들어있는 명령어의 해석을 담당하는 논리회로

- CU (Control Unit) : ID에서 보내진 신호에 따라 명령어를 실행 (clock에 의해 발생)

- WR (Working Register) : 산술 논리연산을 실행할 수 있도록 자료를 저장하고 그 결과를 저장. GPR과 달리 ALU에 직접 연결되어 있음.

- SR (Status Register) : CPU의 상태를 나타내는 특수목적의 레지스터

| 명칭 | 약자 | 설명 |

|---|---|---|

| 영 | Z | zero |

| 부호 | S | sign |

| 오버플로우 | V | overflow |

| 캐리 | C | carry |

| 인터럽트 | I | interrupt |

- 범용 레지스터 (GR, General purpose Register) : WR에서 정보가 용이하게 처리되도록 임시로 자료를 저장

CPU 내부 구조와 명령어 집합

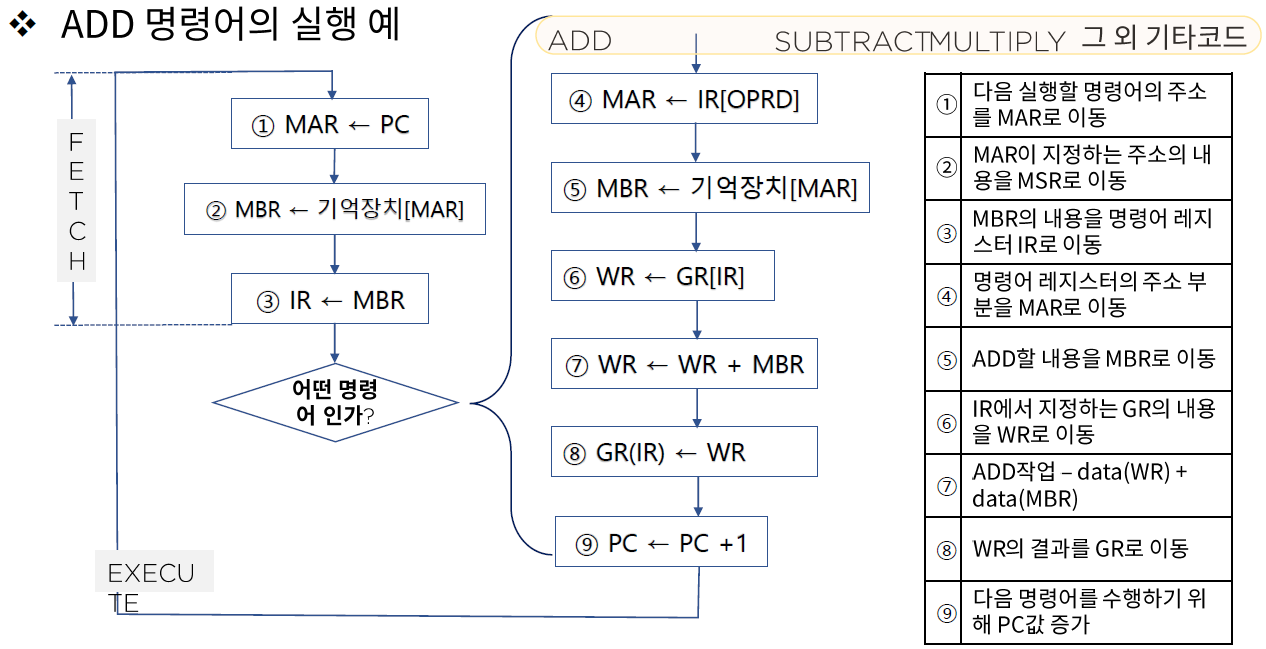

명령어(instruction) 구성과 실행

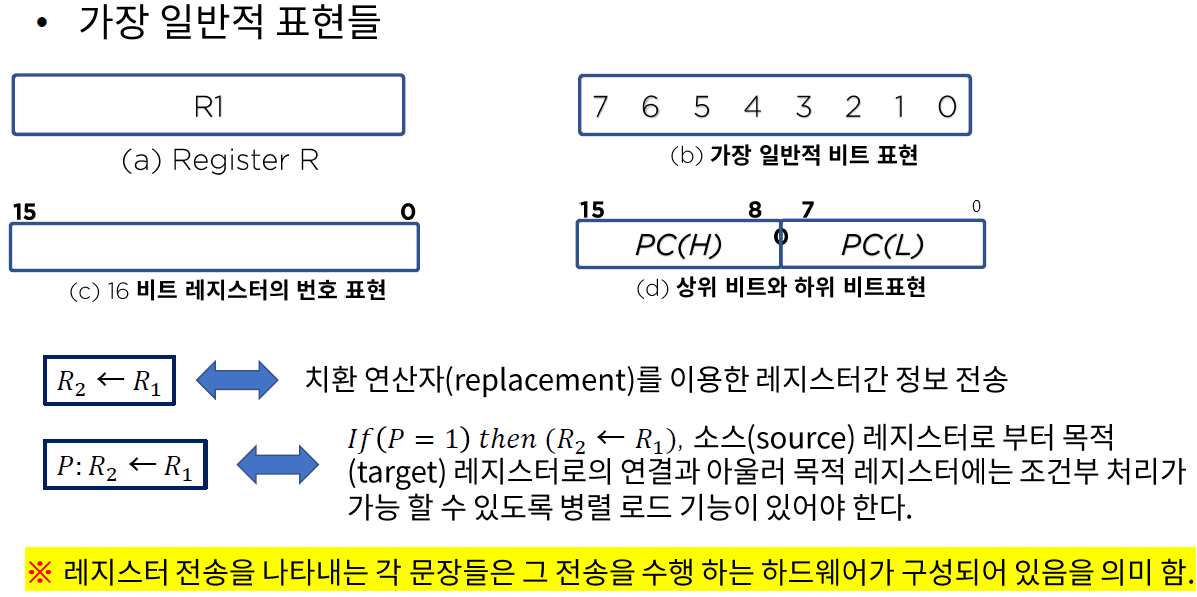

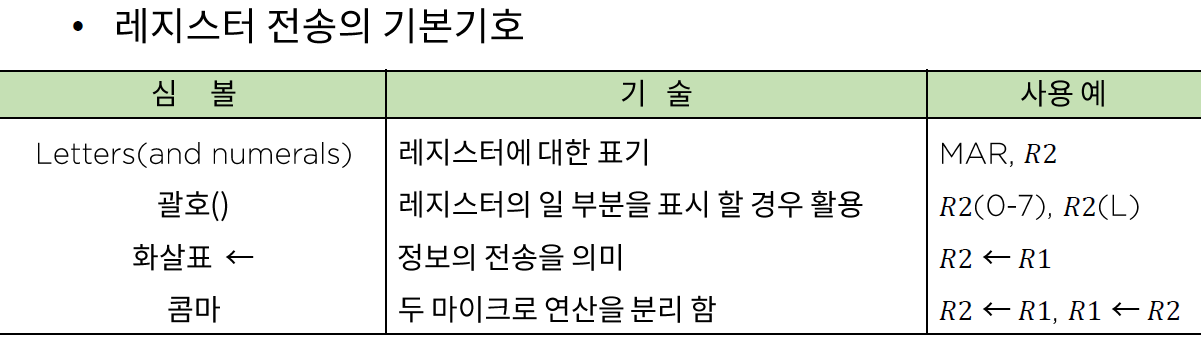

레지스터 전송 언어

마이크로 연산(micro-operation) : Register에 저장된 데이터의 조작을 위해 실행되는 동작으로 하나의 clock pulse 내에서 실행되는 기본적인 동작

- 전송 : 레지스터 사이 이진 정보를 전송

- 산술 : 레지스터에 저장된 수치 데이터에 대해 산술 연산 수행

- 논리 : 레지스터에 저장된 비수치 데이터에 대해 비트 조작 연산 수행

- 시프트 : 레지스터에 저장된 데이터에 대해 시프트 연산 수행

레지스터 전송

CPU(central processing unit) 디자인

CPU 내의 다양한 장치 간 상호 연결 방법

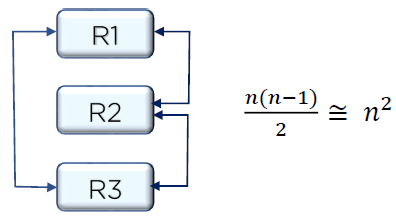

| 직접 연결 | 버스 연결 |

|---|---|

| 연결 복잡도가 장치수의 제곱에 비례 |

공용선에 의한 연결 가장 가성비 높은 연결 방식으로 다양한 관리 방법 존재 |

|

|

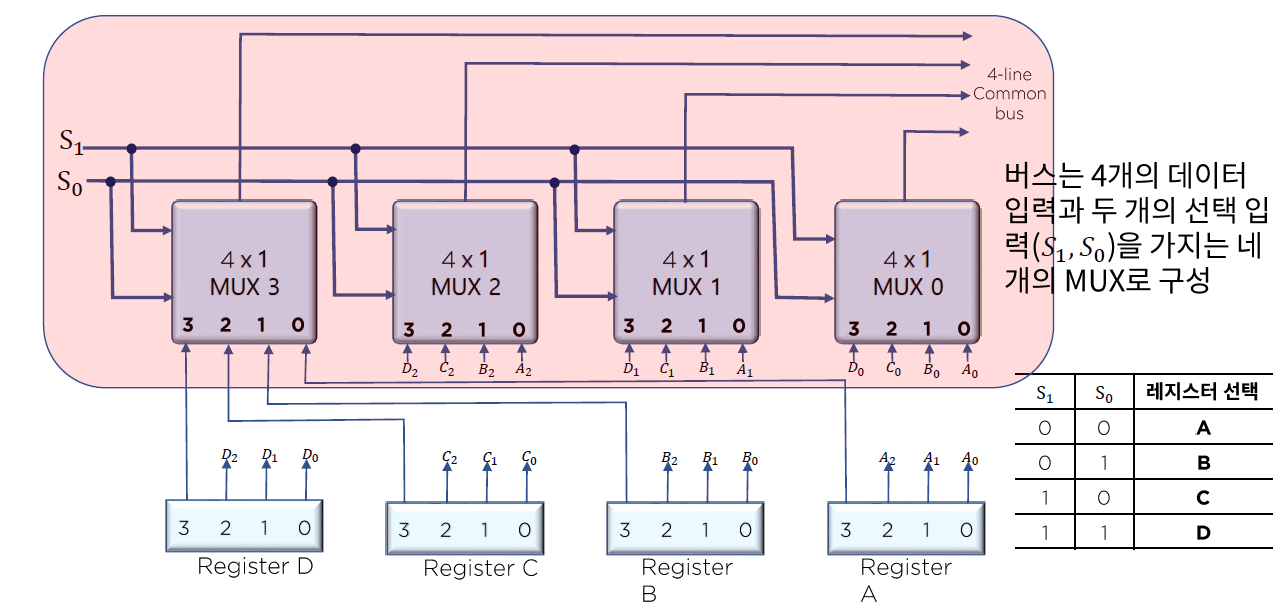

공용선에 의한 레지스터 상호 연결 예 - 멀티 플렉서를 이용

여기서 각 MUX는 각각의 Register의 번지 수에 대응한다.

S0, S1의 입력 조합에 따라서 A-D의 레지스터 중 하나의 레지스터만이 선택된다.

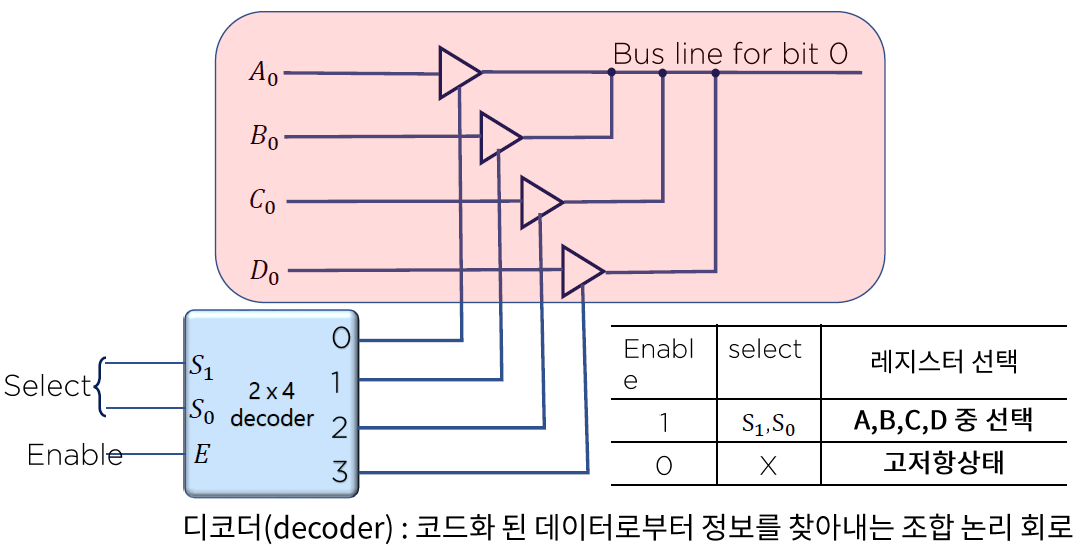

공용선에 의한 레지스터 상호 연결 예 - 3-상태 버스 버퍼

- Enable 값이 0일 경우 어떠한 레지스터도 정보를 보낼 수 없으므로 이전 정보가 유지(기억)된다.

- Enable 값이 1일 경우 S0, S1에 의하여 A-D 중 하나의 레지스터를 선택한다.

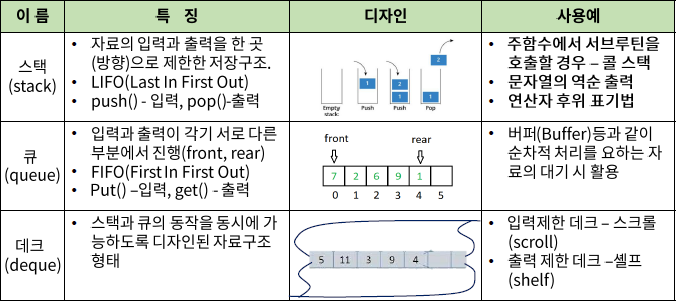

CPU 활용 자료 구조

마이크로 명령과 ALU

마이크로 연산과 ALU

ALU (Arithmetic Logic Unit) : 산술 연산과 논리 연산

- 주로 정수 연산을 처리

- FPU (Floating-Point Unit) : 부동 소수 연산

- 최근에는 ALU가 부동 소수 연산까지 처리

- Parity bit :

- AC (Accumulator) : 처리된 결과를 일시적으로 저장하는 공간

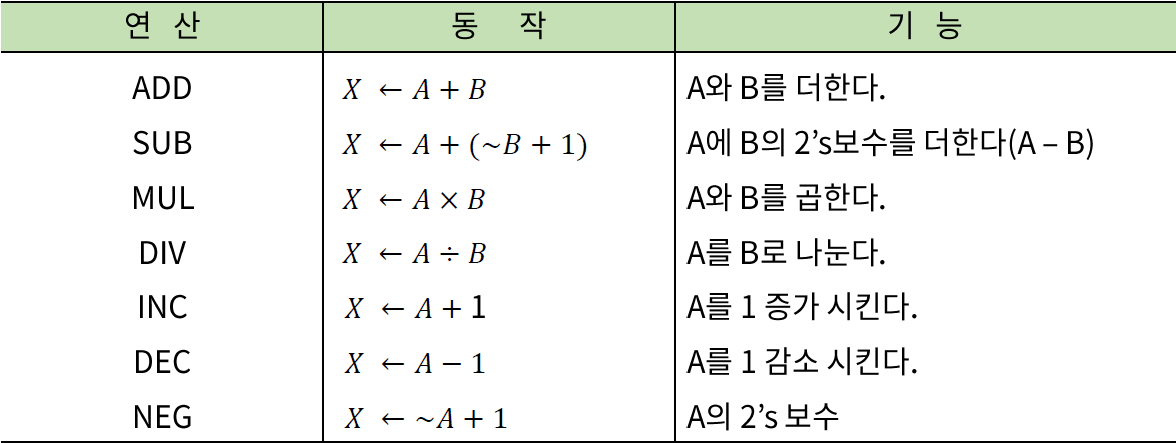

산술 연산

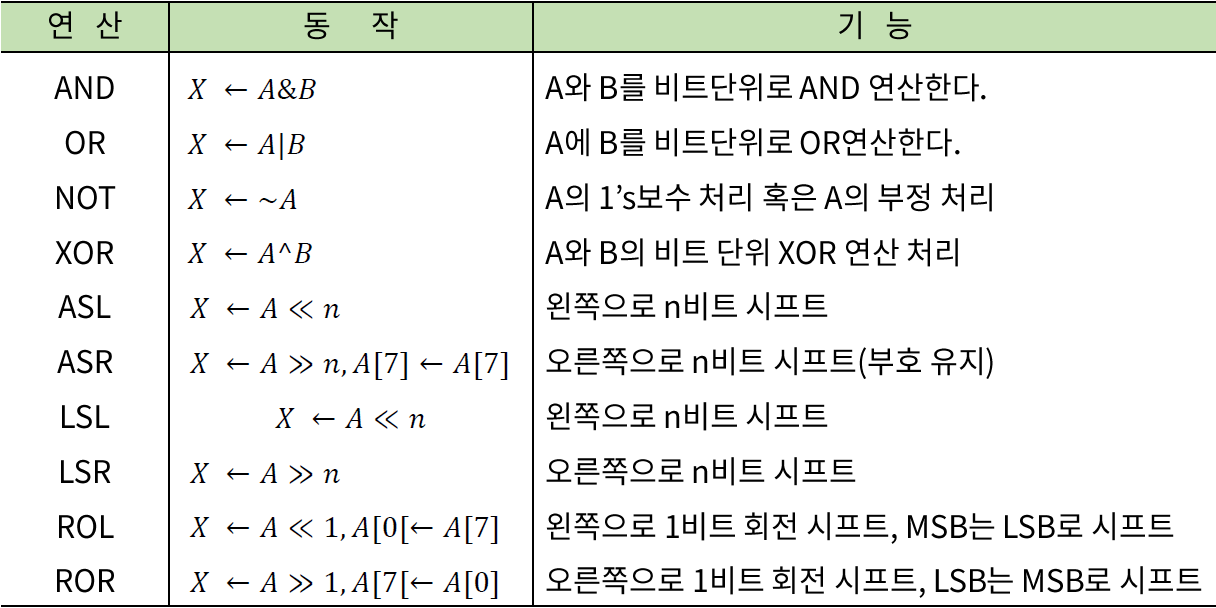

논리 연산

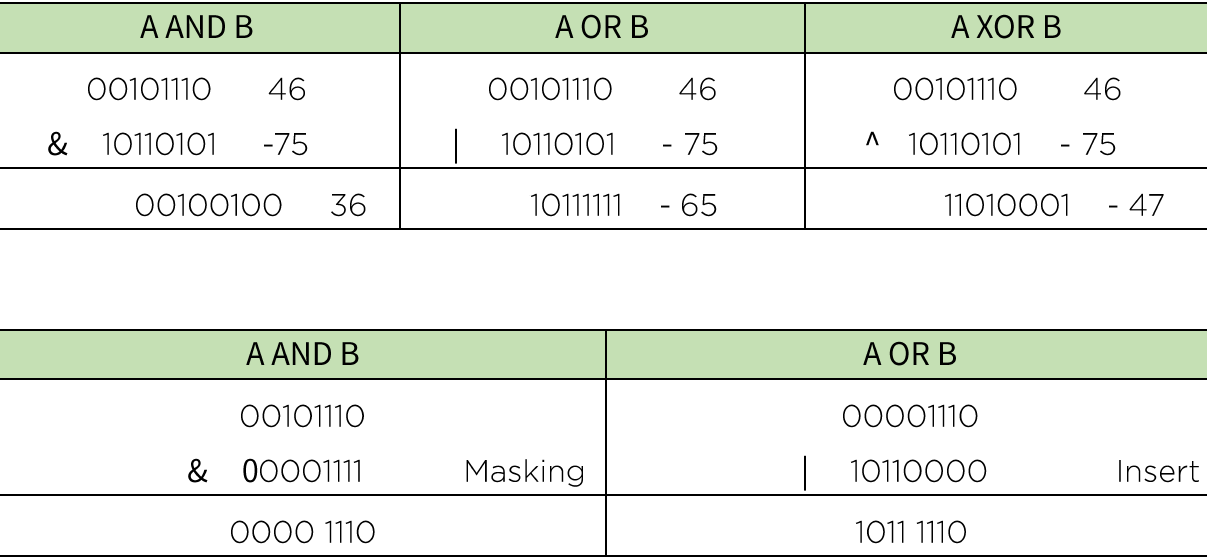

- A : Arithmetic / L : Logical / R : Rotate

- ASL = LSL, ASR != LSR

논리 연산 예

시프트 연산 예

- MSB (Most Significant Bit) / LSB (Least Significant Bit)

마이크로 명령어 집합과 구성

명령어(instruction) 집합

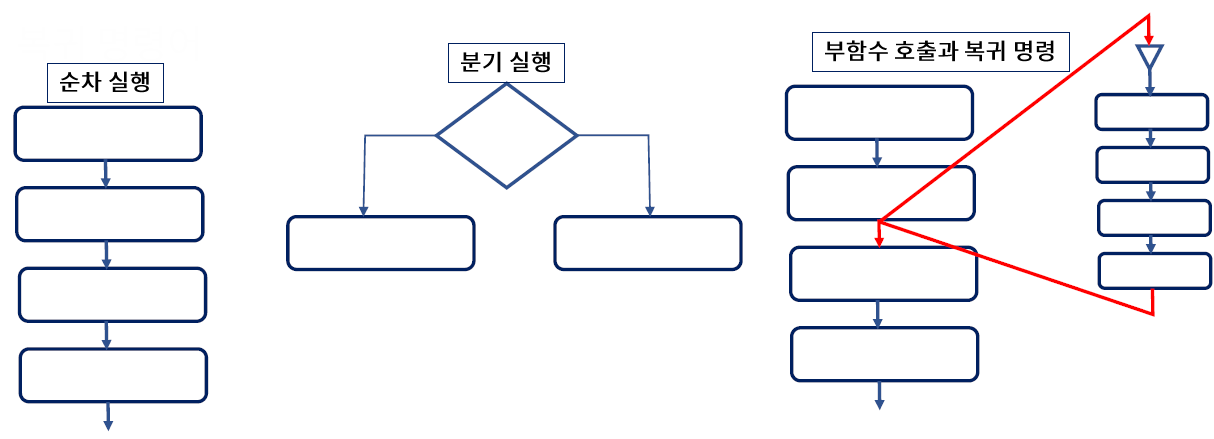

실행 순서에 따른 명령어 분류

- 순차적 실행 명령어 - 전체 명렁어의 70-80%

- 분기 명령어

- 부 함수 호출 명령어

- 복귀 명령어

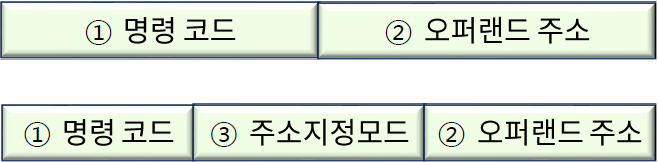

명령어 구문 형식

- 명령 코드 : CPU가 실행할 수 있도록 디자인 된 연산

- 오퍼랜드(operand, 피연산자) : 연산에 사용되는 자료 값, 자료가 저장된 주소에 관한 정보

- 주소 지정 모드(addressing mode) : 오퍼랜드가 저장된 위치를 인덱싱(지정)하는 방법

명령어 집합의 설계

| 설계 관점 | 자연어에 가까운 명령 코드 | 기계 중심의 명령 코드 |

|---|---|---|

| 프로그램의 관점 | - 프로그레밍이 용이 - 전체 프로그램의 길이 감소 - 번역기의 설계 용이 |

- 프로그래밍 규칙이 많아짐 - 프로그램의 길이 증가 - 번역기의 설계가 복잡해짐 |

| CPU 구조 설계 측면 | - 사용언어에 따른 구조적 차이로 인한 오동작 및 처리 어려움 - 명령어의 길이 증가 - 제어장치(ALU, Register 등)의 제어가 매우 복잡해짐 |

- 다양한 업체별 국가별 프로그래밍의 표준화가 가능 - 명령어의 종류 및 길이 등이 간편화 - 제어장치의 제어가 상대적으로 용이 |

현업에서 활용되는 명령어군의 활용 비율

| 명령 코드 | 실행 비율 |

|---|---|

| load, store, move | 38% |

| compare, add, and, sub | 35% |

| condition branch, call, return | 22% |

- 3종류의 명령어가 전체 실행 명령어의 약 90% 이상

주소 지정 모드(addressing mode)

명령어의 구조상 자료가 저장되어 있는 장소를 지정하는 방법이 필요

하드웨어와 소프트웨어의 독립성을 유지하여 유연한 프로그래밍(pointer, indexing 등)을 가능하게 함

- 명령어의 수와 길이를 줄이는 세계적 표준화 기법

- 묵시적 모드(operand가 명령어에 포함되어 있지 않은 특수 모드)

- NOP : No OPeration, 아무 것도 하지 않으므로 오퍼랜드가 필요 없음

- INC : 묵시적 오퍼랜드인 누산기(AC, 1을 증가시킴)의 연산 명령어

- ADD : 스택 구조의 명령어 (스택에 오퍼랜드가 저장)

주소 지정 모드 종류

- Immediate addressing mode (즉시 주소 지정 방식)

- 오퍼랜드가 명령어에 포함되어 있다. ex) MOV R1, #100

- 장점 : 빠름

- 단점 : 명령어 길이가 한정되어 있으므로 수의 크기에 제한이 있음

- Register mode

- 오퍼랜드가 레지스터에 저장되어 있다. ex) ADD R1, R2

- 장점 : 명령어의 주소 필드가 작아도 됨. 메모리 접근이 없어서 매우 빠름

- 단점 : 레지스터 개수 제한

- Direct mode

- 오퍼랜드가 저장된 메모리 주소를 나타냄. ex) MOV R1, 100

- 주소공간이 제한되는 문제

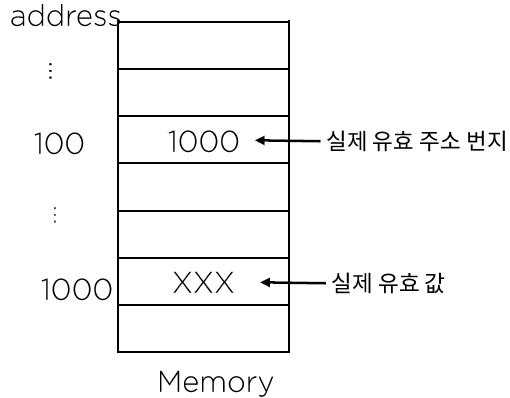

- Indirect mode

- 메모리를 이용하여 간접적으로 주소를 지정함. ex) MOV R1, @100; R1

M[100] or M[100]

M[100] or M[100]  R1

R1

- 메모리를 이용하여 간접적으로 주소를 지정함. ex) MOV R1, @100; R1

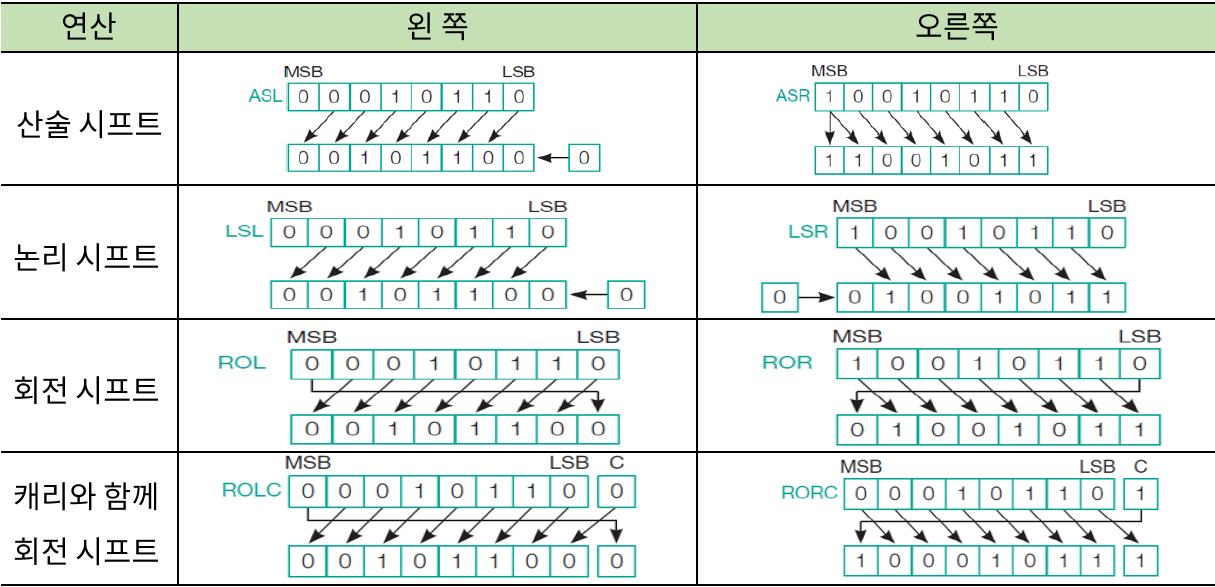

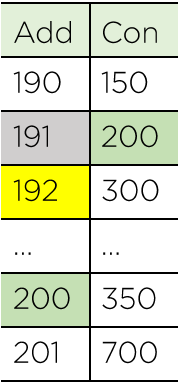

주소 지정 모드 예제

| Memory | 마이크로 명령 | R1에 저장된 값 |

|---|---|---|

|

1. MOV R1, #150 2. MOV R1, R2 3. MOV R1, 192 4. MOV R1, @191 |

1. Immediate adressing mode, R1 = 150, 2. Register mode, R1 = 200 3. Direct mode, R1 = 300 4. Indirect mode, R1 = 350 |